SPECIFICATIONS

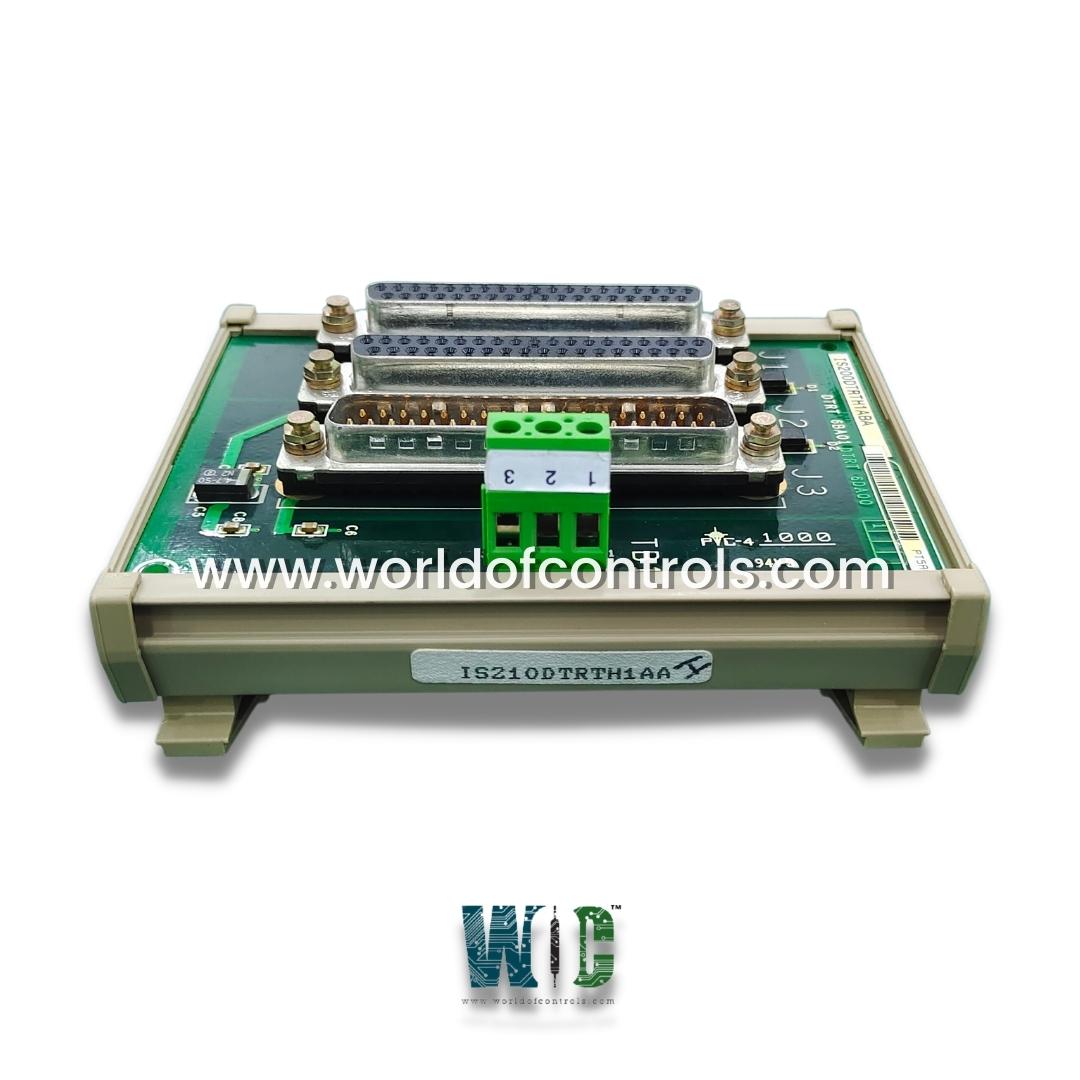

Part No.: IS210DTRTH1AA

Manufacturer: General Electric

Country of Manufacture: United States of America (USA)

Size: 15.9 cm high x 10.2 cm wide

Temperature: -30 to + 65oC

Technology: Surface-mount

Product Type: Primary Trip Relay Interface Board

Availability: In Stock

Series: Mark VI

Functional Description

IS210DTRTH1AA is a Primary Trip Relay Interface Board developed by GE. It is a part of Mark VI control system.The board, designed as a DIN-rail mounted trip transition board, plays a crucial role in facilitating communication and control between the I/O (Input/Output) controller and the DRLY (Relay) board within the system architecture. Its primary function revolves around interfacing these components and redirecting trip functions from the I/O controller to the DRLY board, deviating from the conventional interaction with the TRPG board. Its DIN-rail mounting, interface capabilities between controllers and relays, and support for increased relay control underscore its significance in enhancing system flexibility, control, and capacity within the broader system framework.

Features

- Interface Functionality: The board serves as an intermediary interface, enabling seamless communication between the I/O controller and the DRLY board.

Its primary purpose is to redirect or transition three trip functions originating from the I/O controller to the DRLY board, thus bypassing the usual connection with the TRPG board.

- Mounting and Configuration: It is specifically designed for DIN-rail mounting, allowing for convenient installation and integration into the system's control panel or rack setup.

Its configuration enables the connection of two controllers, collectively controlling a total of six relays on the DRLY board. This configuration expands the capacity for relay control beyond what is typically managed by a single controller.

- Enhanced Trip Functionality: By facilitating the redirection of trip functions to the DRLY board, the board expands the system's trip functionality, allowing for greater flexibility and customization in managing relays and trip-related operations.

- Inter-Board Communication: The board establishes a communication link between the I/O controller and the DRLY board, ensuring efficient relay control and coordination between these components.

- Role in Redundancy and Control Expansion: Its design supports redundancy and scalability within the system, enabling the connection of multiple controllers to increase relay control capacity, offering a reliable means to manage additional relays for expanded system functionality.

Installation

- Mounting the DTRT Board: Designed to slide into a plastic holder specifically intended for DIN-rail mounting. This holder facilitates the secure attachment of the board onto the DIN-rail within the system's control panel or rack setup.

- Connection Setup with I/O Controller and DRLY Board: Three cables are employed to establish connections between the I/O controller and the DRLY board. These cables are plugged into the DC-37 connector on the board.The connections are organized in such a way that the first three DRLY circuits are controlled by the controller connected to J1 on the board. Meanwhile, the subsequent three DRLY circuits are controlled by the controller connected to J2.

- Grounding Connections on Terminal Block TB1: Terminal Block TB1 features an Euro-Block terminal. Within this terminal block, there are provisions for three screws allocated for the SCOM (ground) connection. To ensure proper grounding, it is recommended to connect the grounding wires to these terminals using the provided screws. It's essential to keep the ground connection as short as possible to minimize potential interference and ensure optimal grounding effectiveness.

- Optimizing Grounding Distance: The SCOM (ground) connection on the Euro-Block terminal block (TB1) should ideally maintain a minimal distance to achieve optimal grounding. A shorter distance reduces the potential for interference and improves the efficiency of the grounding mechanism.

Inputs

- Two DC-37 Pin Connectors (J4): These connectors are designated to receive cables from the VTUR (likely referring to a specific component or system). Each connector accommodates cables via a DC-37 pin configuration.

- Trip Relays: Each cable connected to the DC-37 pin connectors (J4) carries signals for three trip relays. This setup indicates that a total of three trip relays per cable are processed or controlled by the DTRT board. Therefore, across the two DC-37 pin connectors, there's a capacity for managing multiple trip relays, possibly related to specific functions or systems within the broader setup.

Outputs

- One DC-37 Pin Connector for Output (Cable to DRLY): The board features a single DC-37 pin connector designated for output. This connector is linked via a cable to the DRLY (Relay) board.

- Total of 6 Trip Relays: The output configuration implies that the board manages or controls a total of six trip relays through the cable connection to the DRLY board. These relays are likely responsible for specific trip functions or actions within the system.

The WOC team is always available to help you with your Mark VI requirements. For more information, please contact WOC.

Frequently Asked Questions

What is IS210DTRTH1AA?

It is a Primary Trip Relay Interface Board developed by GE under the Mark VI series.

What is the purpose of ID devices in terminal board connectors within the system architecture?

Each terminal board connector houses its own ID device containing essential information such as the board's serial number, board type, revision number, and the specific J connector location.

How is the information stored in the ID device utilized within the system?

When the I/O board interrogates the ID device's read-only chip, it reads and verifies the encoded information. This data is crucial for the I/O processor to ensure compatibility and accurate identification of the connected terminal board.

What action is taken if a discrepancy or mismatch is found in the read ID information?

In the event of a mismatch between the read information from the ID chip and the expected parameters stored within the system, a hardware incompatibility fault is generated.