World Of Controls understands the criticality of your requirement and works towards reducing the lead time as much as possible.

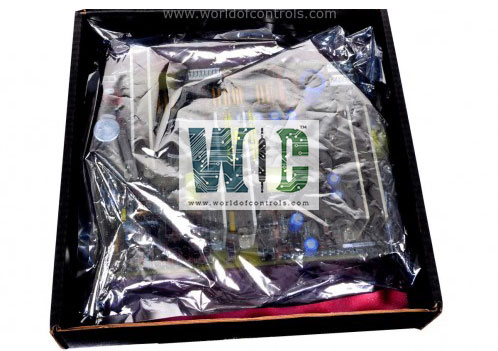

DS200PANAG1ADD - ARCNET LAN Driver Board is available in stock which ships the same day.

DS200PANAG1ADD - ARCNET LAN Driver Board comes in UNUSED as well as REBUILT condition.

To avail our best deals for DS200PANAG1ADD - ARCNET LAN Driver Board, contact us and we will get back to you within 24 hours.

Part No.: DS200PANAG1ADD

Manufacturer: General Electric

Country of Manufacture: United States of America (USA)

Product Type: ARCNET LAN Driver Board

Availability: In Stock

Series: Mark V

DS200PANAG1ADD is an ARCNET LAN Driver Board developed by GE. It is a part of the Mark V control system. LAN Driver Board (PANA) facilitates ARCNET communication specifically designed for COREBUS and Stage Link functionalities. Positioned as a daughterboard on the LBC586P board within the system, the board connects to the AAHA boards via its APL and BPL connectors. Data transmission occurs through these connectors, enabling seamless communication between the PANA board and the AAHA boards.

The WOC team is always available to help you with your Mark V requirements. For more information, please contact WOC.

What is DS200PANAG1ADD?

It is an ARCNET LAN driver board developed by GE under the Mark V series.

What is the purpose of APL on the board?

APL serves as the ARCNET communication link specifically to the AAHA1 board. It facilitates data exchange and communication protocols between the board and the AAHA1 board, enabling seamless integration and operation within the R core system.

What role does BPL play on the board?

BPL functions as the ARCNET communication link to the AAHA2 board. Similar to APL, BPL manages data transmission and communication protocols between the board and the AAHA2 board, ensuring efficient connectivity and operation for ARCNET-based functionalities within the R core.

How does P1 contribute to the functionality?

P1 serves as a bus connection point between the board and the LBC586P processor board. This connection enables data transfer and synchronization between the board and the main processor board (LBC586P), facilitating coordinated operations and system functionality across the R core system.

What is the role of P2 on the board?

P2 also functions as a bus connection to the LBC586P processor board, similar to P1. It provides an additional bus connection point that supports data exchange and synchronization between the board and the main processor board (LBC586P), enhancing overall system performance and integration.